# **Description**

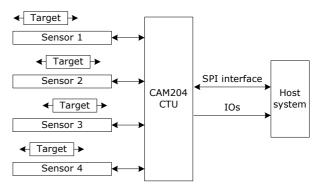

CambridgeIC's Central Tracking Unit (CTU) chip is a single-chip processor for position measurement. It implements the electronic processing for resonant inductive position sensing technology.

The CTU measures the position of contactless, inductively coupled targets relative to sensors that are built from printed circuit boards to CambridgeIC's design. The CTU supports a number of different sensor types, including rotary and linear.

#### **Features**

- Resonant inductive position sensing engine

- Fully ratiometric measurements

- Automatic tuning to target frequency

- SPI communications (slave device)

- · User IOs for position triggers and sample indicators

- Measures up to 4 sensors

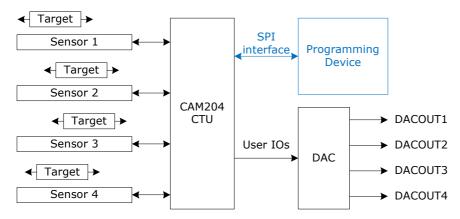

- · Can drive external DAC for up to 4 analog outputs

- Internal software upgradable over SPI

## **Performance**

- Noise Free Resolution 10...14 bits at typical gap

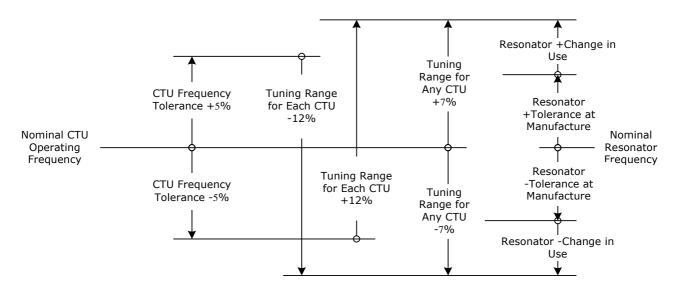

- Tunes to resonators across ±7% frequency range

- < ±0.1% position change across temperature</li>

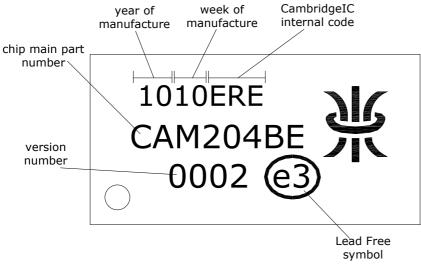

| Product identification |                                 |  |  |  |

|------------------------|---------------------------------|--|--|--|

| Part no.               | Description                     |  |  |  |

| Please                 | CAM204BE in 28-pin SSOP package |  |  |  |

| enquire                | Delivery on Tape and Reel       |  |  |  |

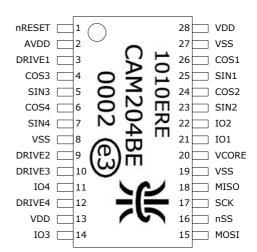

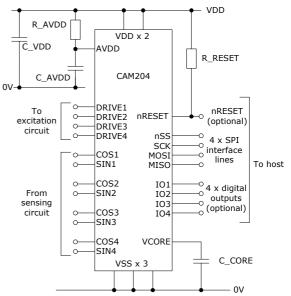

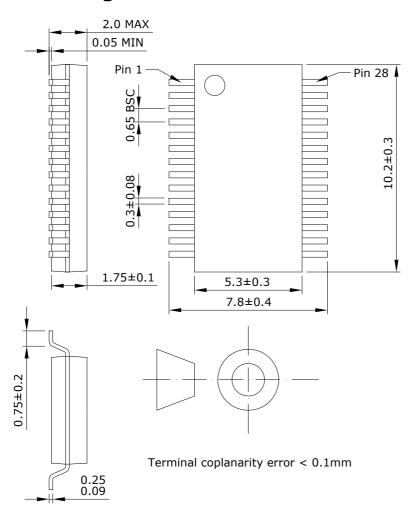

Figure 1 CAM204 28-pin SSOP pinout

Figure 2 CAM204 28-pin SSOP

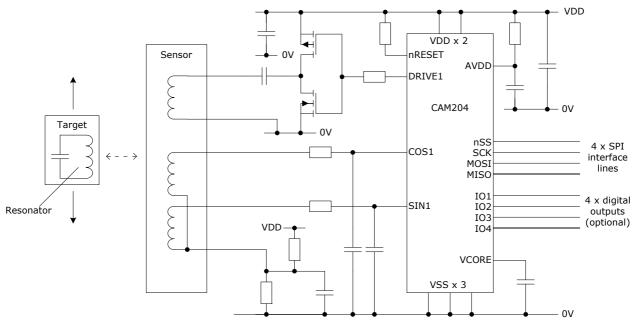

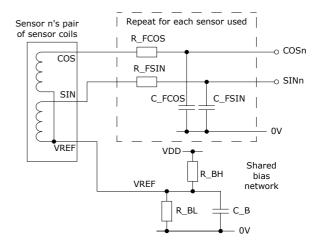

Figure 3 circuit for reading a single Type 1 sensor

# 1 Resonant Inductive Position Sensing Overview

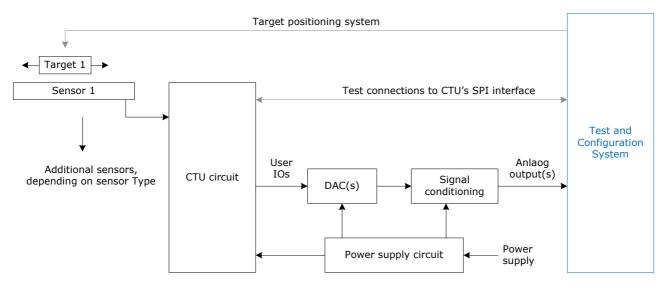

## 1.1 System Components

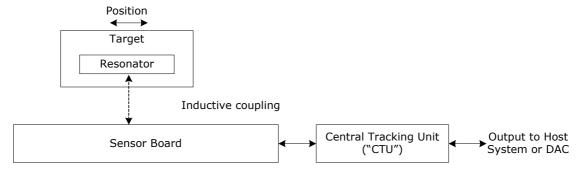

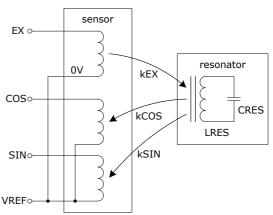

Resonant Inductive Position Sensing is used to track the position of a target without mechanical or electrical contact. The target includes an inductively coupled resonator whose position is measured relative to a sensor.

The sensor comprises a number of coils. It is usually implemented using conventional Printed Circuit Board

(PCB) technology, when it is referred to as a Sensor PCB.

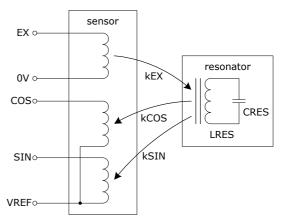

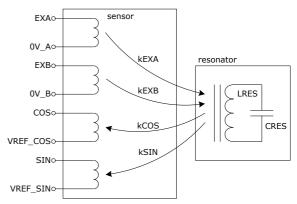

A Central Tracking Unit (CTU) chip interacts with the sensor to power the resonator and to detect the signals that it returns. The detected amplitudes of these signals are processed to calculate position.

Figure 4 resonant inductive position sensing system

# 1.2 Sensor Types

The CAM204 chip can be connected to different Types of sensor. Depending on sensor Type, more than 1 sensor may be connected. They must all be the same Type.

Type 1 sensors comprise 3 coils. The excitation coil is used to power the resonator in the target, and a single pair of sensor coils is used to detect resonator signals. The CTU chip measures their amplitudes and uses them to calculate position.

Type 2 sensors are for measuring linear position over longer distances, and use two pairs of sensor coils to determine "fine" and "coarse" position.

Type 3 sensors are for measuring linear position when the target is allowed to rotate. The rotation axis is along the measuring direction. This enables a target to be embedded in a cylindrical float for liquid level applications, for example.

Type 4 sensors are physically the same as Type 1, except their 0V and VREF connections are shared so that only 4 connections are required between the sensor and CTU circuit

Table 1 lists the sensor types currently supported by the CAM204, and includes section references for more details on each Type.

Table 1 comparison of sensor Types

| Туре | e Number of coils |         | Imber of coils Application                                 |                        | Section number |

|------|-------------------|---------|------------------------------------------------------------|------------------------|----------------|

|      | Excitation        | Sensing |                                                            | of sensors<br>(CAM204) | for details    |

| 1    | 1                 | 2       | Simple linear and rotary sensing                           | 4                      | 4              |

| 2    | 1                 | 4       | Long linear sensors                                        | 1                      | 5              |

| 3    | 2                 | 2       | Linear sensors, freely rotating target                     | 1                      | 6              |

| 4    | 1                 | 2       | Simple linear and rotary sensing, 4-wire sensor connection | 2                      | 7              |

## 1.3 Electronic Interrogation Method

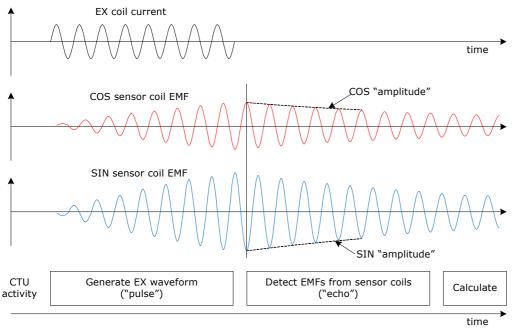

Sensor Types differ in their details, but the same basic measuring principle applies to them all. The CTU generates signals that drive external miniature MOSFETs. These, in turn, drive AC current into the sensor's excitation coil. The excitation coil current generates an AC field which powers the resonator at its resonant frequency. The energy in the resonator is built up during this *pulse*.

Then the current is removed, and the resonator induces decaying EMFs in the sensor coils. The CTU detects the amplitude of this *echo* in each sensor coil. It then uses the amplitude values to calculate position.

The details of the measuring process and calculation depend on sensor Type. In all cases, sensing and calculation are fully ratiometric for immunity to changes in amplitude due to gap, misalignment, temperature, target frequency and supply voltage.

The *pulse echo* interrogation method separates the excitation and detection processes in time. This yields immunity from stray coupling between excitation and sensor coils, and superior sensing performance.

When the sensor Type allows, the CTU may be connected to more than one sensor. In this case, sensors are measured by the CTU in sequence.

Figure 5 electronic measuring process

### 1.4 Resonator Frequency Search and Lock

The CAM204 CTU chip is designed to work with resonators having a high Q-factor (see section 9 for specifications). This means that the AC EMFs generated in sensor coils are large: typically on the order of a volt in amplitude. This yields high resolution and immunity from interference.

The CAM204 CTU chip is also designed for operation across a wide tuning range (see section 9). This means that the resonant frequency need not be particularly well controlled, which saves cost at manufacture and accommodates changes of frequency in use.

In order to achieve both of these beneficial features, the CAM204 can change the frequency it uses to excite and detect the resonator within its tuning range. This means it will always operate on resonance, with optimum signal amplitude.

The first few times the CTU performs a measurement on a particular target (after a reset or target out of range) it performs an optimised search of its frequency range for the target frequency. Once sufficient signal has been detected for frequency lock the CTU performs position measurements and reports VALID.

Once frequency locked, the CTU also calculates resonator frequency. It uses this measurement to tune to the optimum excitation frequency for the next measurement. The CTU also reports resonator frequency over the SPI host interface.

# 2 CAM204 CTU Functional Description

The CAM204 CTU uses sensors built from PCBs to measure the position of contactless targets. These targets comprise an inductively coupled resonant circuit that is energised and detected by the CTU. Sensors can be linear or rotary, and are available in different types for different accuracies and measuring ranges. For more details please see section 1.

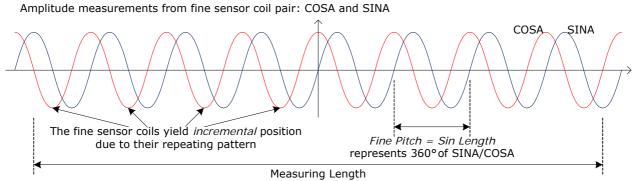

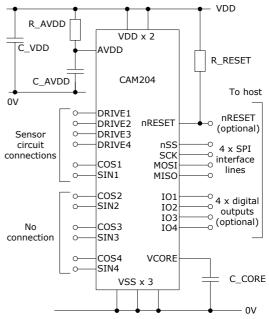

The CAM204 CTU has 4 drive lines and 4 pairs of sensor inputs. Depending on sensor Type, these may be connected to one or more sensors. Sections 4, 5, 6 and 7 illustrate the different configurations possible.

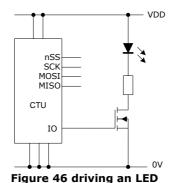

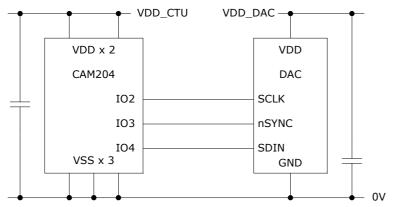

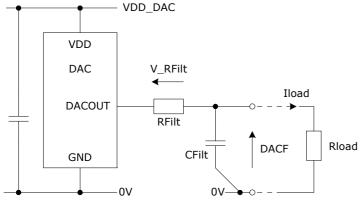

The CAM204 has 4 user configurable IOs. They may be used for signaling when new position samples are available (section 12.7), for controlling LEDs (section

12.10), for position triggers (section 12.11) and/or for driving an external DAC (section 13).

Communication with a host device is by a simple register-based SPI interface in which the CTU is a slave device. Alternatively, once appropriately configured over the SPI interface, the CAM204 may run autonomously (section 12.16).

The CAM204 includes internal FLASH memory used to store its application firmware. This may be updated over the SPI interface using an on-chip bootloader (section 14).

Table 2 summarises CAM204 pin functions.

Table 2

| Signal Name                | Туре                                     | Description                                                                                                                              |

|----------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| VDD (x2)                   | Power                                    | Positive supply voltage.                                                                                                                 |

| AVDD                       | Analog Input                             | Analog supply voltage, decoupled from VDD.                                                                                               |

| VSS (x3)                   | Power                                    | 0V connection and common return for sensor inputs.                                                                                       |

| VCORE                      | Power                                    | Output of on-chip regulator, requires external decoupling capacitor to VSS.                                                              |

| nRESET                     | Digital Input                            | Hardware reset, active low. Requires 10K resistor to VDD. Connection to host device is optional.                                         |

| nSS                        | Digital Input                            | SPI Interface line: Slave Select, active low.                                                                                            |

| SCLK                       | Digital Input                            | SPI Interface line: Serial Clock.                                                                                                        |

| MOSI                       | Digital Input                            | SPI Interface line: Master Out, Slave In.                                                                                                |

| MISO                       | Digital Output                           | SPI Interface line: Master In, Slave Out.                                                                                                |

| IO1, IO2, IO3, IO4         | Digital Outputs<br>(optional open drain) | User configurable IO. Can be used for position triggers, to signal new or VALID samples, for driving LEDs and/or driving an external DAC |

| DRIVE1 - DRIVE4            | Digital Outputs                          | Used to drive external MOSFETs for powering the excitation coil(s) of resonant inductive position sensors.                               |

| COS1 - COS4<br>SIN1 - SIN4 | Analog Inputs                            | Used to sense the sensor coil outputs of resonant inductive sensors.                                                                     |

# 3 Electrical Characteristics

# 3.1 Operating Characteristics

**Table 3 operating characteristics**

| Item                              | Min     | Max   | Comments                    |

|-----------------------------------|---------|-------|-----------------------------|

| Operating Supply Voltage VDD      | 2.65V   | 3.60V |                             |

| Operating Temperature             | -40°C   | 85°C  | Max +125°C for CAM204BE     |

| VDD start voltage relative to VSS |         | 0.1V  | For reliable power on reset |

| VDD rise rate relative to VSS     | 0.5V/ms |       |                             |

## 3.2 Absolute Maximum Ratings

Table 4 absolute maximum ratings

| Item                                                | Max             | Comments                     |

|-----------------------------------------------------|-----------------|------------------------------|

| Ambient temperature under bias                      | -40°C to +100°C | -40°C to +135°C for CAM204BE |

| Voltage between VDD and VSS                         | -0.3V to +4.0V  |                              |

| Voltage between IO1-4 and SPI lines relative to VSS | -0.3V to +6.0V  |                              |

| Current into or out of Digital Output               | 25mA            |                              |

## 3.3 Digital Input Specifications

The specifications of Table 5 apply to digital inputs: the SPI interface lines nSS, SCLK and MOSI and the nRESET line.

Table 5 digital input specifications

| Item                  | Min                 | Max        |

|-----------------------|---------------------|------------|

| Input Low             | VSS                 | 0.15 x VDD |

| Input High            | (0.24 x VDD) + 0.8V | 5.5V       |

| Input leakage current |                     | ±1µA       |

## 3.4 Digital Output Specifications

The specifications of Table 6 apply to digital outputs: the 4 user configurable IO pins IO1-IO4 and the SPI interface line MISO. IO1-IO4 can be set to *digital* or *open drain*, see section 11.3. MISO is always open drain.

Table 6 digital output specifications

| i ubic o digital output opcomentions     |      | _    |                     |

|------------------------------------------|------|------|---------------------|

| Item                                     | Min  | Max  | Comments            |

| Output Low Voltage                       |      | 0.4V | IOL = 5mA           |

| Output High Voltage (digital setting)    | 2.1V |      | VDD=2.5V IOH = -2mA |

|                                          | 3.0V |      | VDD=3.6V IOH = -3mA |

| Output High Current (open drain setting) |      | ±1µA |                     |

## 3.5 Application Memory Characteristics

The CAM204 includes a processor with FLASH memory. This can be updated with new Application Code over its SPI interface, see section 13. It can also be updated with new Configurable Defaults, see section 12.16. FLASH memory related specifications are in Table 7 below.

Table 7 application memory characteristics

| Item                    | Min      | Max  | Comments                          |

|-------------------------|----------|------|-----------------------------------|

| Number of FLASH updates |          | 2000 | Across Operating Supply           |

| Retention time          | 20 years |      | Voltage and Operating Temperature |

# 4 Type 1 Sensor Application

## 4.1 Type 1 Sensor Overview

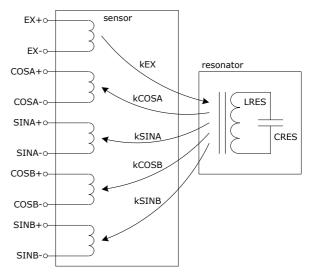

Type 1 sensors are available for linear and rotary position sensing using resonant inductive technology. They have a simple, 3-coil design with the equivalent circuit illustrated in Figure 6.

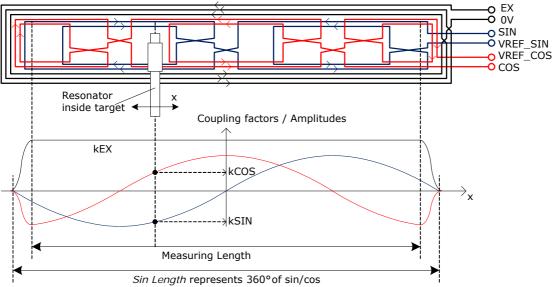

Figure 7 illustrates the design of a Type 1 linear sensor. An outer excitation coil, EX, is for powering a resonator inside an inductively coupled target. Two sensor coils, SIN and COS, are for measuring signals returned from the resonator.

Up to 4 Type 1 sensors may be connected to a CAM204. Each may have its own or multiple targets, or targets may be shared between them.

Figure 6 equivalent circuit, Type 1 sensor

Figure 7 sketch of coils in a Type 1 linear sensor

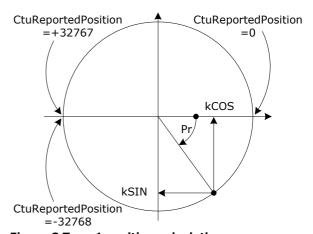

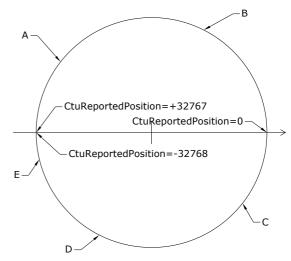

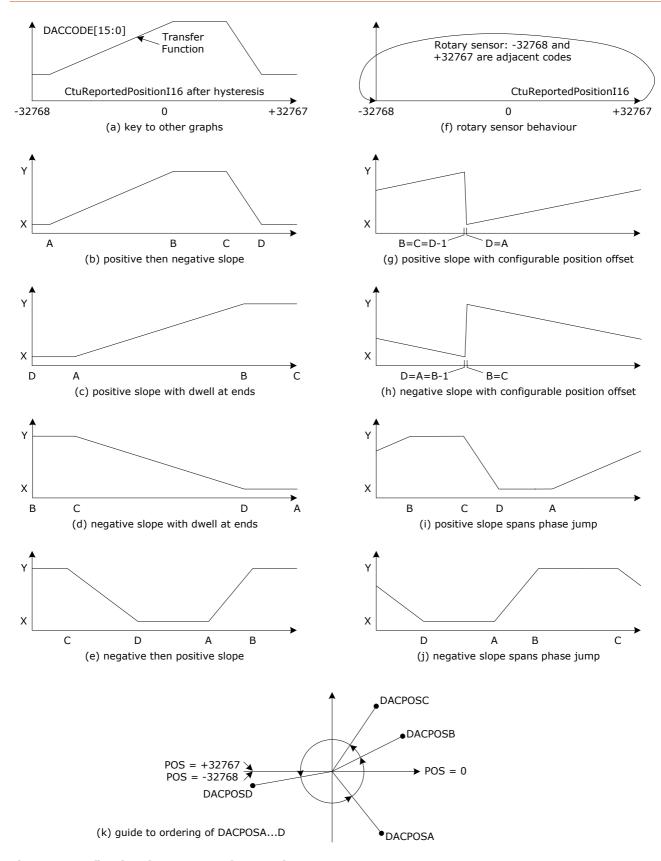

To determine the position of a target relative to a sensor, the CTU performs a measurement of SIN and COS amplitudes as described in section 1.3. It then uses these to calculate the angle of the (kCOS, kSIN) vector. This angle represents position. The CTU's reported position output is the 16-bit word CtuReportedPosition. This is scaled such that 360° of spatial angle is represented by 65536 reported units.

Position calculation is illustrated in Figure 8. Pr is the spatial angle. The values shown match the target positioned as in Figure 7.

Figure 8 Type 1 position calculation

# 4.2 Circuit Schematics, Type 1

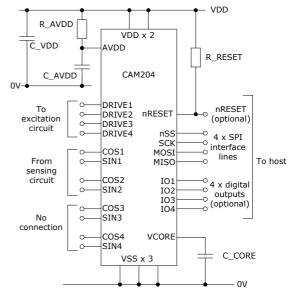

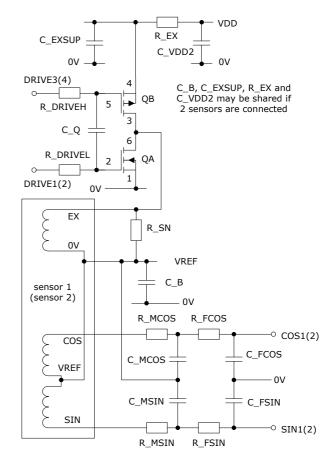

Figure 9 shows how the CAM204's supplies should be connected, the chip's connections to the host and to the excitation and sensing circuits. Component values are listed in Table 8.

VCORE is an external connection to an on-chip 2.5V regulator. This pin requires an external decoupling capacitor. It must not be connected to other circuitry.

AVDD is the analog supply input to the CAM204, and is used as a reference voltage. The values of R\_AVDD and C\_AVDD are important for the CAM204 to operate to full specification.

nRESET requires a pull-up resistor to VDD for the CAM204's on-chip power on reset circuit to operate successfully. nRESET may optionally be connected to an open drain output from the host, and used as an active-low reset line for the chip. This simplifies bootloader operation (section 14).

MISO is an open drain output, and requires a pull-up resistor of  $4.7k\Omega$  if this is not provided by the host.

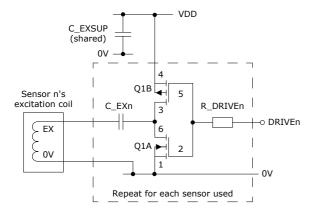

Figure 10 excitation circuit, Type 1

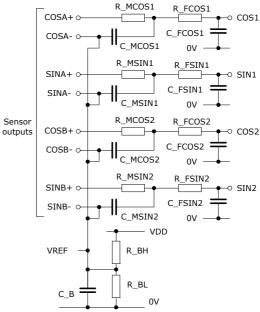

Sensor coil connections to the CAM204 are illustrated in Figure 11. There is a shared bias network, plus an RC filter per sensor coil input to the CAM204. All circuit values quoted in Table 8 are important for function and performance to specification. VREF should not be generated by other means.

Figure 9 CAM204 connections, Type 1

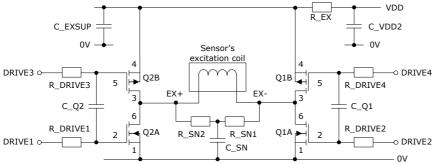

The CAM204 uses an external complementary MOSFET pair to drive current into each sensor's excitation coil. Figure 10 shows the excitation circuit. When more than one sensor is connected, decoupling capacitor C\_EXSUP can be shared across sensors providing connections are kept short. The MOSFET pair, resistor R\_DRIVEn and capacitor C\_DRIVEn are all repeated for each sensor connected.

MOSFET pair Q1 is available as a single miniature device, see Table 8 for the part required. Resistor(s)  $R\_DRIVEn$  limit the operating speed of the MOSFET pair, to minimise capacitively coupled emissions. Capacitor(s)  $C\_EXn$  remove the DC voltage component at the MOSFET drains from the voltage applied to the excitation coil.

Figure 11 sensor coil connections, Type 1

# 4.3 Components Required, Type 1

Table 8 lists the components used in the CTU circuits of section 4.2, and their values. It also includes how many are required, depending on the number of Type 1 sensors connected.

Table 8 components required for Type 1 sensors

| Circuit Ref                   | Value          | Tolerance    | Number required for |           |           |           |

|-------------------------------|----------------|--------------|---------------------|-----------|-----------|-----------|

|                               |                |              | 1 sensor            | 2 sensors | 3 sensors | 4 sensors |

| R_RESET                       | 10kΩ           | ±5%          |                     |           | 1         |           |

| R_AVDD                        | 100Ω           | ±5%          |                     |           | 1         |           |

| R_DRIVEn                      | 330Ω           | ±5%          | 1                   | 2         | 3         | 4         |

| R_FCOSn/SINn                  | 2.7kΩ          | ±1%          | 2                   | 4         | 6         | 8         |

| R_BH                          | 68kΩ           | ±1%          |                     |           | 1         |           |

| R_BL                          | 47kΩ           | ±1%          |                     |           | 1         |           |

| C_VDD                         | 470nF          | ±10%         |                     |           | 1         |           |

| C_AVDD                        | 4.7μF          | ±10%         |                     |           | 1         |           |

| C_CORE                        | 10μF, ESR < 3Ω | -50% / +100% |                     |           | 1         |           |

| C_EXSUP                       | 10μF, ESR < 3Ω | -50% / +100% |                     |           | 1         |           |

| C_EXn                         | 470nF          | ±10%         | 1                   | 2         | 3         | 4         |

| C_FCOSn/SINn                  | 47pF           | ±5%          | 2                   | 4         | 6         | 8         |

| C_B                           | 100nF          | ±10%         |                     |           | 1         |           |

| Q1                            | FDY4000CZ      |              | 1                   | 2         | 3         | 4         |

| Number of external components |                |              | 16                  | 23        | 30        | 37        |

# 4.4 Sample Time and Rate, Type 1

Sample Time and Sample Rate are defined in section 12.8.

There are two Sample Rate values in Table 9. The first is the maximum rate at which sensors can be measured and position triggers generated. This is measured in continuous sampling mode, with INTERVAL set to 0 (see section 11.2). In this case there is no time for SPI transactions.

The second Sample Rate specification is the maximum rate at which a sensor's position can be read over the SPI interface. The SPI Communication Time is assumed to be  $120\mu s$ .

When the CTU is used to sample more than one sensor at a time, sensors are scanned sequentially. Achievable sample rate is reduced accordingly.

The maximum sample time and minimum sample rate occur when the target's resonant frequency is at the low end of the tuning range for any CTU (see Table 21).

Table 9 sample time and rate, Type 1

| Item                                       | Min    | Max   |

|--------------------------------------------|--------|-------|

| Sample Time                                |        | 800µs |

| Maximum Sample Rate<br>(position triggers) | 1.2kHz |       |

| Maximum Sample Rate<br>(SPI interface)     | 1.1kHz |       |

# 4.5 Current Consumption, Type 1

The CAM204's supply current depends on the rate at which it is sampling position. Illustrative values are in Table 10. These figures include the current required for the excitation circuit and the biasing network  $R\_BH$  and  $R\_BL$ .

There is a power down mode under host control activated over the SPI interface by writing to the PWRDN bit (see section 11.1).

# 4.6 Reproducibility, Type 1

The CAM204 relies only on the geometry of coils printed on a PCB for position sensing, and is fully ratiometric. It is therefore largely immune to temperature changes, and there is minimal chip to chip variability.

Table 11 specifies worst case reproducibility across chips and temperature. Figures are based on the average of a number of successive measurements, so that noise present in individual readings is rendered insignificant.

The reproducibility of successive position readings is measured as the noise present in the CAM204's data

# 4.7 Noise Free Resolution, Type 1

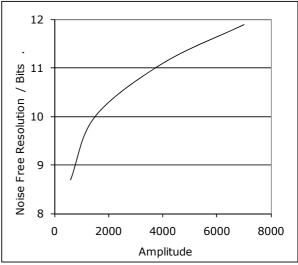

Position resolution is not limited by the number of bits reported over the SPI interface (16 for a Type 1 sensor). A more useful measure of resolution is Noise Free Resolution. This describes how many different positions the CAM204 can distinguish, considering the noise present in the lower bits of its output.

The Noise Free Resolution is given by Equation 1, and is based on the standard deviation of Reported Position results (calculated from Equation 5) with a stationary target. Equation 1 is based on the standard Noise Free Resolution definition for an ADC. See, for example, "The Data Conversion Handbook" By Walter Allan Kester, Analog Devices Inc, 2005.

$PkPkNoise = 6.6 \times StandardDeviation$

Noise Free Resolution =  $log_2 \left| \frac{SinLength}{PkPkNoise} \right|$

#### Equation 1

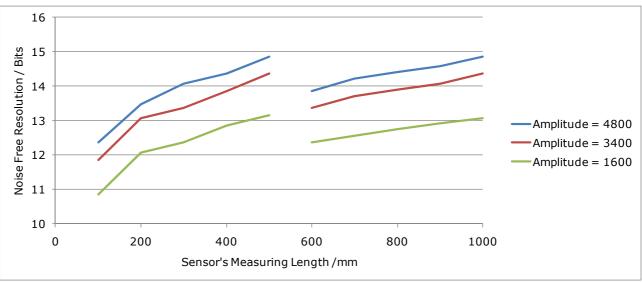

The CAM204's Noise Free Resolution improves with Amplitude, as illustrated in Figure 12. Amplitude depends on a number of factors including the type of sensor and target, and the gap between them. See sensor datasheets for more information. A typical Amplitude at a sensor's nominal operating gap is 3000, so that typical Noise Free Resolution is 10 bits.

Table 10 current consumption, Type 1

| Function          | Typical current at VDD = 3.3V |

|-------------------|-------------------------------|

| Sampling at 1kHz  | 33mA                          |

| Sampling at 100Hz | 12mA                          |

| Idle              | 9mA                           |

| PWRDN bit set     | 50µA                          |

stream, and hence Noise Free Resolution. This is addressed in section 4.7.

Table 11 reproducibility, Type 1

| Reproducibility<br>(Amplitude ≥ 2000)                     | Max   |

|-----------------------------------------------------------|-------|

| Across CAM204 chips, constant temperature                 | ±0.1% |

| Across temperature range -40°C to +85°C, same CAM204 chip | ±0.1% |

When used with an external DAC, the Noise Free Resolution of the analog output is a combination of the CAM204's value and that of the DAC. The analog circuitry used to condition and distribute the analog signal will also contribute noise, and can be minimised through careful analog design.

Figure 12 Noise Free Resolution, Type 1

# 5 Type 2 Sensor Application

## 5.1 Type 2 Sensor Overview

Type 2 sensors are available for linear position sensing using resonant inductive technology. They differ from Type 1 sensors in having two pairs of SIN/COS sensing coils as illustrated in Figure 13.

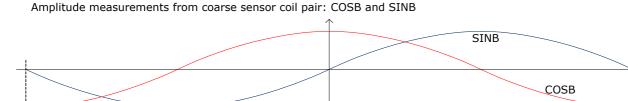

The COSA/SINA pair are the "fine" coils, and the COSB/SINB pair are the "coarse" coils. Figure 14 illustrates how the coil amplitudes depend on position. The CTU calculates "coarse" and "fine" position in a similar way to Type 1 (section 4.1).

"Coarse" position is absolute, since Coarse Pitch is less than the Measuring Length. However, this measurement has poor accuracy and resolution.

"Fine" position is *incremental*: it can locate the target over the Fine Pitch distance unambiguously, but the measurement repeats at greater distances. This measurement has the advantage of high precision, however.

To achieve an output which is both precise and absolute, the CTU combines "fine" and "coarse" position measurements. Two methods are available, depending on the setting of the incremental enable bit INCE, as detailed in section 5.2.

The CAM204 CTU chip can be connected to one Type 2 sensor, as illustrated in section 5.4.

Figure 13 equivalent circuit, Type 2 sensor

Coarse Pitch represents 360° of SINB/COSB

Figure 14 coil amplitudes as a function of position, Type 2 sensor

# 5.2 Type 2 Sensor Operating Modes

When the host sets the INCE (*incremental enable*) bit to 0 the CTU always takes a fresh measurement from both fine and coarse sensor coils to generate each new reported position. The CTU sets INCF (*incremental flag*) to 0 to indicate incremental mode was not used for the measurement. The INCE and INCF bits are located in the SCW host register, see section 11.9.

When the host sets the INCE bit to 1, incremental mode is enabled. If there is no target present, the CTU's behaviour is the same as INCE=0. It sets INCF to 0, and takes readings from both the coarse and fine sensor coils. When a target is in range and a first valid measurement has been taken, subsequent measurements are based on measurements from the fine sensor coils alone, and INCF is set to 1. In

incremental mode, the CTU still reports full absolute position. It uses the previous reported position as its approximate estimate of absolute position, which is then refined with the new incremental data from the fine sensor coils.

The advantage of incremental mode is a shorter Sample Interval, since measurements from the coarse sensor coils are not required.

However there is one well understood and highly repeatable failure mode in incremental mode: *skipping a fine period*. This will occur if the target's position changes by more than the *Fine Period Skip Distance* between CTU position measurements. This is given by:

Fine Period Skip Distance =

$$\frac{Fine\ Pitch}{2}$$

- (peak to peak position noise) - (peak to peak position error)

Equation 2

For the purposes of this equation, peak to peak position noise and error must be taken as absolute

Fine Period Skip Distance =  $0.4 \times Fine Pitch$  Equation 3

For a typical Fine Pitch of 50mm, the Fine Period Skipping Distance is therefore 20mm. To prevent *skipping a fine period*, it is recommended that the host only sets INCE to 1 when the interval between successive CTU position measurements is 2ms or less, AND the velocity of the target is known to be less than 10ms<sup>-1</sup>. These values will yield the required 20mm maximum.

For a sensor with a Fine Pitch of 100mm, the Fine Period Skipping Distance is 40mm. The recommended

extreme values, and the following working definition is recommended:

maxim interval and velocity are 2ms and 20ms<sup>-1</sup> respectively.

As an additional precaution, the host may opt to alternate between a run of measurements taken with INCE=1 and single measurements taken with INCE=0. This will not prevent the "skipping a fine period" failure mode, but any position offset will be eliminated immediately with an INCE=0 measurement.

#### 5.3 BA Mismatch Output

The CTU reports the results of a Type 2 sensor measurement in the 6 results registers RESA-RESF, described in section 11.11. In addition to position, amplitude and relative frequency measurements, the CTU also reports *BA Position Mismatch*. This is a diagnostic output for the healthiness of the CTU's absolute position calculation.

When INCE=0, BA Position Mismatch is the difference between the B (coarse) and A (fine) position calculations. When INCE=1, BA Position Mismatch is the difference between the most recent position measurement and the one before. BA Position

Mismatch is a signed 16-bit value (-32768 to +32767). The value 0 represents perfect health, and extreme positive and negative values are bad. When INCE=0, "bad" means highly inaccurate measurements on fine and/or coarse tracks due to a circuit or sensor PCB fault. When INCE=1, "bad" means excessive distance between successive measurements due to excess time interval and/or velocity.

BA Position Mismatch is scaled in the same way as Reported Position (Equation 5). The extreme values - 32768 and +32767 therefore represent  $\pm$ (Fine Pitch/2).

# 5.4 Circuit Schematics, Type 2

Figure 15 shows how the CAM204's supplies should be connected, the chip's connections to the host and to the excitation and sensing circuits. Component values are listed in Table 12.

VCORE is an external connection to an on-chip 2.5V regulator. This pin requires an external decoupling capacitor. It must not be connected to other circuitry.

AVDD is the analog supply input to the CAM204, and is used as a reference voltage. The values of R\_AVDD and C\_AVDD are important for the CAM204 to operate to full specification.

nRESET requires a pull-up resistor to VDD for the CAM204's on-chip power on reset circuit to operate successfully. nRESET may optionally be connected to an open drain output from the host, and used as an active-low reset line for the chip. This simplifies bootloader operation (section 1413).

MISO is an open drain output, and requires a pull-up resistor of  $4.7k\Omega$  if this is not provided by the host.

Figure 15 CAM204 connections, Type 2

Figure 16 excitation circuit, Type 2

The CAM204 uses an external MOSFET "H" bridge to drive a Type 2 sensor's excitation coil. Figure 16 shows the excitation circuit. MOSFET pairs Q1 and Q2 are each available as a single miniature device, see Table 12. The gate drive circuit uses 2 resistors and 1 capacitor per side, and is designed to enable the CTU to drive the bridge output to a high impedance state. The resistors R DRIVE limit the operating speed of the MOSFETs, to minimise capacitively coupled emissions. The capacitors C O1 and C O2 prevent excessive shoot-through current during switching. The network R\_SN1, R\_SN2 and C\_SN absorb the energy in the excitation coil on the transition from low to high impedance. The energy required for each pulse of excitation current is stored in C\_EXSUP. R\_EX limits the peak charging current.

Figure 17 shows the components required for the sensor coil inputs to the CTU. Each of the 4 coil inputs has two stages of RC filtering formed by the components with prefix R\_F2, C\_F2, R\_F and C\_F. The reference voltage VREF is generated by the network R\_BH, R\_BL and CB. VREF should not be generated by other means.

Figure 17 sensor coil connections, Type 2

# 5.5 Components Required, Type 2

Table 12 lists the component values and numbers required for the schematics of 5.4. The filter components connected to the CTU's sensor 1 inputs are important for reproducibility, and the table includes two grades for them: A and B. Grade A yields

the least system to system reproducibility error due to component differences. Grade B components are more cost effective. Grade A and B reproducibility error is compared in Table 13.

Table 12 components required for a Type 2 sensor

| Circuit Ref  | Value              | Tolerance    |                   | Number   |

|--------------|--------------------|--------------|-------------------|----------|

|              |                    | Grade A      | Grade B           | required |

| R_RESET      | 10kΩ               | =            | ±5%               | 1        |

| R_AVDD       | 100Ω               | =            | ±5%               | 1        |

| R_DRIVE1/2   | 1.6kΩ              | =            | ±5%               | 2        |

| R_DRIVE3/4   | 330Ω               | =            | ±5%               | 2        |

| R_EX         | 1Ω                 | =            | ±5%               | 1        |

| R_SN1/2      | 100Ω               | =            | ±5%               | 2        |

| R_MCOS1/SIN1 | 100Ω               | ±0.1%        | ±1%               | 2        |

| R_MCOS2/SIN2 | 100Ω               | =            | ±1%               | 2        |

| R_FCOS1/SIN1 | 1kΩ                | ±0.1%        | ±1%               | 2        |

| R_FCOS2/SIN2 | 1kΩ                | =            | ±1%               | 2        |

| R_BH         | 15kΩ               | =            | ±1%               | 1        |

| R_BL         | 10kΩ               | =            | ±1%               | 1        |

| C_VDD        | 470nF              | ±10%         |                   | 1        |

| C_AVDD       | 4.7μF              | ±10%         |                   | 1        |

| C_CORE       | 10μF, ESR < 3Ω     | -50%         | / +100%           | 1        |

| C_EXSUP      | 100μF, ESR < 100mΩ | -50% / +100% |                   | 1        |

| C_VDD2       | 100μF, ESR < 100mΩ | -50%         | / +100%           | 1        |

| C_Q1/2       | 1nF                | ±            | 10%               | 2        |

| C_SN         | 10nF               | ±            | 10%               | 1        |

| C_MCOS/SIN1  | 2.2nF              | ±1%          | ±5%               | 2        |

| C_MCOS/SIN2  | 2.2nF              | ±5%          |                   | 2        |

| C_FCOS/SIN1  | 220pF              | ±1%          | ±5%               | 2        |

| C_FCOS/SIN2  | 220pF              | ±5%          |                   | 2        |

| C_B          | 470nF              | ±10%         |                   | 1        |

| Q1/2         | FDY4000CZ          |              |                   | 2        |

|              |                    | Number of ex | ternal components | 38       |

Table 13 reproducibility error due to filter components

| Grade Reproducibility as |                 | Reproducibility in µm |                    |  |  |  |

|--------------------------|-----------------|-----------------------|--------------------|--|--|--|

|                          | % of Fine Pitch | Fine Pitch = 50mm     | Fine Pitch = 100mm |  |  |  |

| Α                        | ±0.03%          | ±15µm                 | ±30µm              |  |  |  |

| В                        | ±0.17%          | ±85µm                 | ±170µm             |  |  |  |

# 5.6 Sample Time and Rate, Type 2

Sample Time and Sample Rate are defined in section 12.8. The SPI Communication Time is assumed to be  $160\mu s$ .

The state of the INCF bit reflects the operating mode, see section 5.2. INCF=1 ("incremental") yields faster sampling.

The maximum sample time and minimum sample rate occur when the target's resonant frequency is at the low end of the tuning range for any CTU (see Table 21).

Table 14 sample time and rate, Type 2

| Item                                | INCF state | Min    | Max    |

|-------------------------------------|------------|--------|--------|

| Sample Time                         | 0          |        | 1530µs |

| Maximum Sample Rate (SPI interface) |            | 590Hz  |        |

| Sample Time                         | 1          |        | 840µs  |

| Maximum Sample Rate (SPI interface) |            | 1000Hz |        |

# 5.7 Current Consumption, Type 2

Power supply current consumption is lowest when the CTU is not sampling, and typical values are in Table 15. These figures include the current required for the biasing network R\_BH and R\_BL. The power down mode draws the lowest current and is activated over the SPI interface by writing to the PWRDN bit (see section 11.1).

Table 15 typical supply current, VDD = 3.3V

| Function      | Typical |

|---------------|---------|

| Idle          | 9mA     |

| PWRDN bit set | 150µA   |

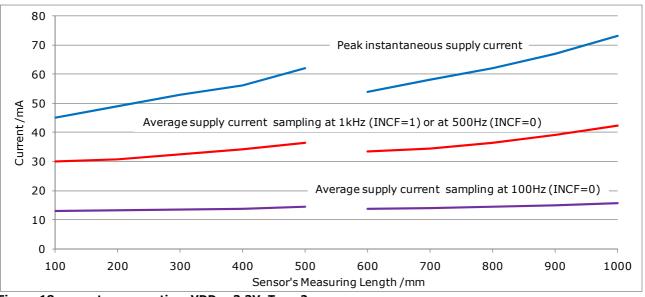

Figure 18 illustrates typical power supply current consumption when sampling, for sensors of different Measuring Length. The peak instantaneous supply current occurs when INCF=0. The values shown are for a power supply source resistance of  $1\Omega$ . Average supply current depends on sample rate and operating mode.

Figure 18 current consumption, VDD = 3.3V, Type 2 sensors

# 5.8 Noise Free Resolution, Type 2

Noise Free Resolution describes how many different positions the CAM204 can distinguish, considering the noise present in the lower bits of its output. It is generally a more useful measure than interface resolution for a system having excess interface resolution, as described in section 4.7. The typical data in Figure 19 is based on Equation 4. This uses the standard deviation of a number of measurements as a robust measure of peak to peak noise.

$PkPkNoise = 6.6 \times StandardDeviation$

Noise Free Resolution

$$= log_2 \left[ \frac{Measuring \ Length}{PkPkNoise} \right]$$

**Equation 4**

Figure 19 Noise Free Resolution, Type 2

# 6 Type 3 Sensor Application

## 6.1 Type 3 Sensor Overview

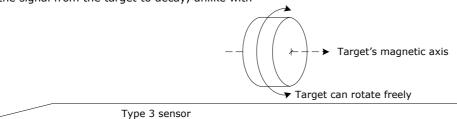

Type 3 sensors measure the linear position of a freely rotating target, as illustrated in Figure 21.

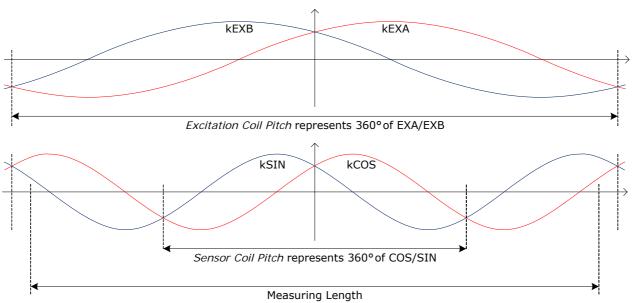

The magnetic axis of the target points along the measuring direction. This means that a uniform excitation coil, as used in Type 1 and 2 sensors, is not possible. Instead, there are two excitation coils, EXA and EXB. They are sinusoidally patterned, as illustrated in Figure 22. At least one of the excitation coils couples to the target, whatever its location along the measuring length.

Sensor coils are also sinusoidally patterned. They have a different pitch to the excitation coils, chosen to enable absolute position measurement.

The CTU detection process is similar to the one described in section 1.3. The CTU first pulses current into excitation coil EXA and measures the return signals in COS and SIN. It then repeats the measurement with EXB. When combined, the measurements yield full absolute position. The CTU must leave enough time between each measurement for the signal from the target to decay, unlike with

Type 1 and 2 sensors. This makes the measuring process slower for Type 3 sensors than for other types.

The equivalent circuit of a Type 3 sensor is shown in Figure 20. The CAM204 CTU chip can be connected to one Type 3 sensor, as illustrated in section 6.2.

Figure 20 equivalent circuit, Type 3 sensor

Figure 21 Type 3 sensors work with freely rotating targets

Figure 22 coil coupling factors as a function of position, Type 3 sensor

# 6.2 Circuit Schematics, Type 3

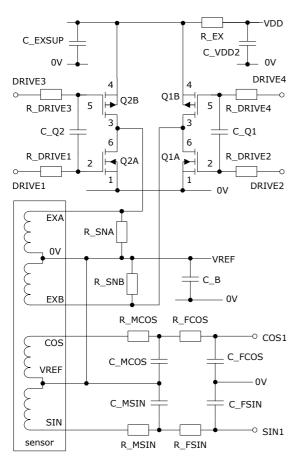

Figure 23 shows how the CAM204's supplies should be connected, the chip's connections to the host and to the sensor circuit. Component values are listed in Table 16.

VCORE is an external connection to an on-chip 2.5V regulator. This pin requires an external decoupling capacitor. It must not be connected to other circuitry.

AVDD is the analog supply input to the CAM204, and is used as a reference voltage. The values of R\_AVDD and C\_AVDD are important for the CAM204 to operate to full specification.

nRESET requires a pull-up resistor to VDD for the CAM204's on-chip power on reset circuit to operate successfully. nRESET may optionally be connected to an open drain output from the host, and used as an active-low reset line for the chip. This simplifies bootloader operation (section 14).

MISO is an open drain output, and requires a pull-up resistor of  $4.7k\Omega$  if this is not provided by the host.

Figure 24 sensor circuit, Type 3

Figure 23 CAM204 connections, Type 3

Each of the sensor's two excitation coils is driven from a complementary MOSFET pair, available in a single miniature device. Resistors R\_DRIVE limit the slew rate of the MOSFET drains, to minimise capacitively coupled emissions. Capacitors C\_Q prevent excessive shoot-through current during switching.

The energy required for each pulse of excitation current is stored in C\_EXSUP. R\_EX limits the peak charging current. Resistors R\_SN absorb the energy in their respective excitation coils on the transition from low to high bridge output impedance.

Capacitor C\_B is charged to approximately half supply rail during excitation pulses so that the excitation coils are driven with current in both directions by MOSFET pairs Q1/2. The reference voltage developed, VREF, is also used to bias the CTU's sensor inputs during detection.

Two stages of RC filtering are used between the sensor coils and CTU inputs, using the network formed by resistors R\_MCOS/SIN, C\_MCOS/SIN, R\_FCOS/SIN, C\_FCOS/SIN.

# 6.3 Components Required, Type 3

Table 16 lists the components required for connecting a Type 3 sensor to the CAM204 CTU chip, using the schematics of section 6.2.

Table 16 components required for a Type 3 sensor

| Circuit Ref                      | Value          | Tolerance    | Number required |  |

|----------------------------------|----------------|--------------|-----------------|--|

|                                  |                |              |                 |  |

| R_RESET                          | 10kΩ           | ±5%          | 1               |  |

| R_AVDD                           | 100Ω           | ±5%          | 1               |  |

| R_DRIVE1/2                       | 1.6kΩ          | ±5%          | 2               |  |

| R_DRIVE3/4                       | 330Ω           | ±5%          | 2               |  |

| R_EX                             | 22Ω            | ±5%          | 1               |  |

| R_SN1/2                          | 1kΩ            | ±5%          | 2               |  |

| R_MCOS/SIN                       | 220Ω           | ±1%          | 2               |  |

| R_FCOS/SIN                       | 1kΩ            | ±1%          | 2               |  |

| C_VDD                            | 470nF          | ±10%         | 1               |  |

| C_AVDD                           | 4.7μF          | ±10%         | 1               |  |

| C_CORE                           | 10μF, ESR < 3Ω | -50% / +100% | 1               |  |

| C_EXSUP                          | 10µF           | ±10%         | 1               |  |

| C_VDD2                           | 10µF           | ±10%         | 1               |  |

| C_Q1/2                           | 1nF            | ±10%         | 2               |  |

| C_MCOS/SIN                       | 1nF            | ±5%          | 2               |  |

| C_FCOS/SIN                       | 220pF          | ±5%          | 2               |  |

| C_B                              | 4.7μF          | ±10%         | 1               |  |

| Q1/2                             | FDY4000CZ      |              | 2               |  |

| Number of external components 27 |                |              |                 |  |

#### 6.4 Sample Time and Rate, Type 3

Sample Time and Sample Rate are defined in section 12.8. The SPI Communication Time is assumed to be 160µs. The maximum sample time and minimum sample rate occur when the target's resonant frequency is at the low end of the tuning range for any CTU (see Table 21).

The Sample Time for Type 3 sensors is much longer than for Types 1 and 2, since the CTU must allow time for resonator signal decay from each different

## 6.5 Current Consumption, Type 3

Typical supply current for Type 3 sensor operation is in Table 15. Figures include the current required for the excitation circuit.

There is a power down mode under host control activated over the SPI interface by writing to the PWRDN bit (see section 11.1).

excitation coil, so that their relative amplitudes are consistent and accuracy is maintained.

Table 17 sample time and rate, Type 3

| Item                                   | Min   | Max   |

|----------------------------------------|-------|-------|

| Sample Time                            |       | 7.8ms |

| Maximum Sample Rate<br>(SPI interface) | 125Hz |       |

Table 18 typical supply current, VDD = 3.3V

| Function          | Typical current |

|-------------------|-----------------|

| Sampling at 100Hz | 17mA            |

| Idle              | 9mA             |

| PWRDN bit set     | 10μΑ            |

# 7 Type 4 Sensor Application

# 7.1 Type 4 Sensor Overview

Type 4 sensors work in the same way as Type 1 sensors, described in section 4.1, and have the same coil arrangement. The difference is that their 0V and VREF terminals are connected together, as illustrated in Figure 25. This enables a 4-wire connection from the CTU circuit to sensor.

The CAM204 CTU chip can sense up to 2 Type 4 sensors, as shown below.

# 7.2 Circuit Schematics, Type 4

Connections to the CAM204 chip itself are as shown in Figure 15. The sensor circuit is shown in Figure 26. This is for a sensor connected to the CAM204's sensor 1 inputs. A sensor may also be connected to the sensor 2 inputs, with the CTU signal connections shown in brackets. Two sensors may be connected. In this case, the components C\_B, C\_EXSUP, R\_EX and C\_VDD2 may be shared.

Each sensor's excitation coil is driven from a complementary MOSFET pair, available in a single miniature device. Resistors R\_DRIVE limit the slew rate of the MOSFET drains, to minimise capacitively coupled emissions. Capacitors C\_Q prevent excessive shoot-through current during switching.

The energy required for each pulse of excitation current is stored in C\_EXSUP. R\_EX limits the peak charging current. Resistors R\_SN absorb the energy in their respective excitation coils on the transition from low to high bridge output impedance.

Capacitor C\_B is charged to approximately half supply rail during excitation pulses so that the excitation coils are driven with current in both directions by the MOSFET(s). The reference voltage developed, VREF, is also used to bias the CTU's sensor inputs during detection

Two stages of RC filtering are used between the sensor coils and CTU inputs, using the network formed by resistors R\_MCOS/SIN, C\_MCOS/SIN, R\_FCOS/SIN, C\_FCOS/SIN.

Figure 25 equivalent circuit, Type 4 sensor

Figure 26 sensor circuit, Type 4

# 7.3 Components Required, Type 4

Table 19 lists the components required for connecting a Type 3 sensor to the CAM204 CTU chip, using the combined schematics of Figure 15 and Figure 26.

Table 19 components required for type 4 sensors

| Circuit Ref | Value          | Tolerance           | Number required for |           |  |

|-------------|----------------|---------------------|---------------------|-----------|--|

|             |                |                     | 1 sensor            | 2 sensors |  |

| R_RESET     | 10kΩ           | ±5%                 |                     | 1         |  |

| R_AVDD      | 100Ω           | ±5%                 |                     | 1         |  |

| R_DRIVELn   | 1.6kΩ          | ±5%                 | 1                   | 2         |  |

| R_DRIVEHn   | 330Ω           | ±5%                 | 1                   | 2         |  |

| R_EX        | 4.7Ω           | ±5%                 |                     | 1         |  |

| R_SNn       | 1kΩ            | ±5%                 | 1                   | 2         |  |

| R_MCOS/SINn | 220Ω           | ±1%                 | 2                   | 4         |  |

| R_FCOS/SINn | 1kΩ            | ±1%                 | 2                   | 4         |  |

| C_VDD       | 470nF          | ±10%                |                     | 1         |  |

| C_AVDD      | 4.7μF          | ±10%                |                     | 1         |  |

| C_CORE      | 10μF, ESR < 3Ω | -50% / +100%        |                     | 1         |  |

| C_EXSUP     | 10µF           | ±10%                |                     | 1         |  |

| C_VDD2      | 10μF           | ±10%                |                     | 1         |  |

| C_Qn        | 1nF            | ±10%                | 1                   | 2         |  |

| C_MCOS/SINn | 1nF            | ±5%                 | 2                   | 4         |  |

| C_FCOS/SINn | 220pF          | ±5%                 | 2                   | 4         |  |

| C_B         | 4.7μF          | ±10%                |                     | 1         |  |

| Qn          | FDY4000CZ      |                     | 1                   | 2         |  |

|             | Number of e    | external components | 22                  | 35        |  |

# **8 Circuit Layout**

#### 8.1 CAM204 Circuit

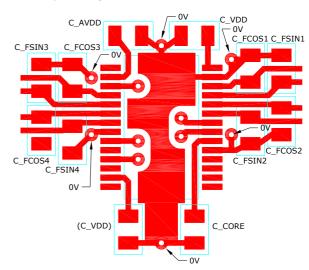

Connections between the CAM204's VSS pins should be as wide and short as possible. This is preferably by vias near each pin to a ground plane layer on the PCB.

Connections between the CAM204's VDD pins should also be kept as wide and as short as possible. C\_VDD should be placed right next to the chip, with short and wide connections to both VSS and VDD pins. If the connection between VDD pins is difficult, an alternative is to use two decoupling capacitors C\_VDD, one adjacent to each VDD pin.

The remaining decoupling capacitors, C\_CORE, C\_AVDD and filter capacitors connected to the CAM204's SIN/COS1-4 pins must all be placed as close as possible to the CAM204, with short connections to the chip and VSS.

Figure 27 shows a possible layout in the area of the CAM204, and includes the capacitors which need to be kept close to that chip.

The excitation circuit should be laid out to minimise the length of the current path from the VDD end of C\_EXSUP through each half of each MOSFET bridge and back to the 0V end of C\_EXSUP. Where a single excitation decoupling capacitor C EXSUP is shared

between multiple MOSFETs, the MOSFETs of all circuits should be placed close together so that all such current path lengths are minimised.

Figure 27 component layout around CAM204

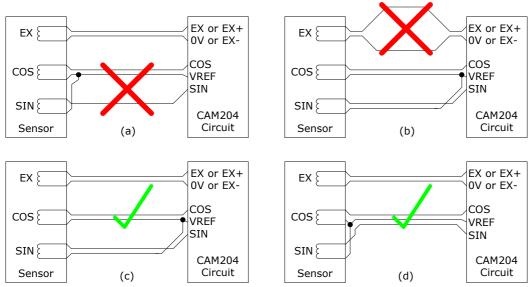

# 8.2 Sensor Connections Avoiding Loops

Sensors that operate using resonant inductive technology use coils to pick up signals from a resonator in the target. These coils are specially patterned for accurate position sensing. To avoid inaccuracy, and to minimise the effect of any interference, the size of any additional loops formed by

connecting conductors must be minimised. Figure 28 (a) and (b) illustrate incorrect connections, where connecting conductors form loops. Figure 28 (c) and (d) illustrate correct connecting options, where the loop size is minimised.

Figure 28 connection between sensor and CAM204 circuit

# 8.3 Recommended PCB Track Design for Sensor Connection

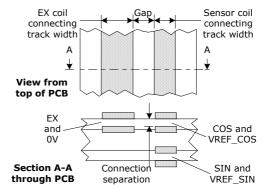

Figure 29 illustrates how connections may be made using conductors on a 4-layer PCB. Loop sizes are minimised by running the connections for each coil on adjacent layers of the PCB, so that one runs on top of the other.

The excitation coil connecting track widths should preferably be wide to minimise resistance. A loop resistance of less than  $0.5\Omega$  is preferable. PCBs with "1oz" copper (34µm thick) have a surface resistivity of  $0.5m\Omega/\text{square}$ , so connections can be up to 1000 squares long. (The number of squares is the overall length divided by the width). For example, a pair of 200mm long connections has an overall length of 400mm. If the width of each is 0.5mm, then the number of squares is 800.

Sensor coil connecting tracks are less critical. The connecting loop resistance should ideally be less than  $5\Omega$ .

If the gap between excitation and sensor connections illustrated in Figure 29 is small and the connections are long, there may be a significant level of coupling between the two, causing small errors in reported position. Examples of limiting values are shown in Table 20.

Table 20

| Connection separations = 0.2mm  Min connecting track Min Max |         |       |        |  |  |

|--------------------------------------------------------------|---------|-------|--------|--|--|

| width                                                        | Sensors | Gap   | Length |  |  |

| 0.2mm                                                        | 0.1mm   | 0.1mm | 100mm  |  |  |

| 0.8mm                                                        | 0.1mm   | 0.4mm | 400mm  |  |  |

Figure 29 connections using PCB traces

# 9 Resonator Detection

The CTU is designed to lock onto and track the resonant frequency of inductively coupled resonators inside targets.

The CTU measures the position of each sensor's target in turn. Each time, it also estimates its resonant frequency, providing there is sufficient signal amplitude. If the resonant frequency changes, the CTU changes its excitation frequency to match.

Following power on reset, or if the previous measurement was invalid, the CTU searches its tuning range for the target, trying different excitation frequencies until it achieves lock.

Table 21 lists CTU specifications related to target detection.

Table 21

| Item                                 | Min  | Тур      | Max | Comments                             |

|--------------------------------------|------|----------|-----|--------------------------------------|

| Nominal CTU Operating Frequency      |      | 187.5kHz |     |                                      |

| CTU Centre Frequency Tolerance       |      |          | ±5% | Across Operating Supply Voltage and  |

| Tuning Range for Each CTU            | ±12% |          |     | Operating Temperature                |

| Tuning range for Any CTU             | ±7%  |          |     |                                      |

| Resonator Q-factor                   | 60   |          | 180 |                                      |

| Number of samples before lock        |      |          | 9   | Following invalid sample or power on |

| Minimum Amplitude (Type 1&3 sensors) | 250  |          | 500 | For CTU to report VALID              |

| Minimum Amplitude (Type 2 sensors)   | 250  |          | 700 |                                      |

Figure 30 illustrates system frequency budgets. The tuning range for any CTU is derived from the CTU frequency tolerance and the tuning range for each CTU, and is the range of resonator frequencies that all CTU chips can tune to. Resonator Frequency Tolerance at Manufacture plus Resonator Frequency Change in Use in use must remain within this range for reliable detection.

The CTU reports relative frequency in its results registers accessible over its SPI interface (see section 11.11). The result is for diagnostic purposes and is approximate. To improve reproducibility of the CTU's relative frequency indication, the host should perform a CTU reset after power on, and the PWRDN state should be avoided (see section 11.1).

Figure 30 illustration of frequency tolerance budgets

# 10 SPI Hardware

#### 10.1 Overview

This section describes how data is written to, and read back from, the CAM204 CTU, over its SPI interface. Each read or read-write operation accesses one or more of the CTU's internal registers. The next section, section 11, details the function of each of the available registers. Section 12 describes how to control the CTU to perform sensor position measurements by accessing

these registers over the SPI interface, and how to configure the CTU's IO pins to implement position trigger signals.

For communication with a host system, the CAM204 CTU is always an SPI slave. All communication is initiated by the host.

#### 10.2 Data Transfer Method

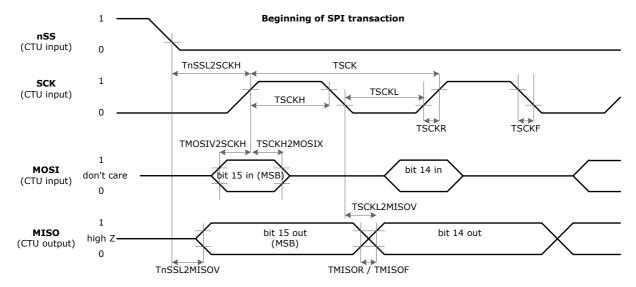

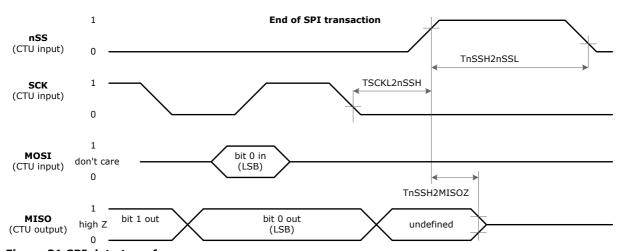

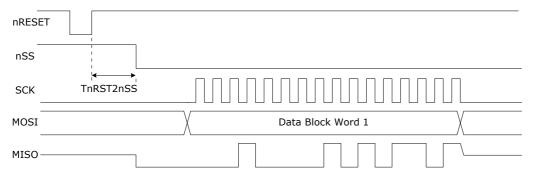

The CAM204 CTU always operates as an SPI slave device. The host device signals a data transfer by driving nSS low. It clocks data presented on the MOSI line into the CTU on the positive going transition of SCK. The CTU outputs successive data bits on its MISO line on negative going SCK transitions. This is commonly referred to as SPI Mode 0.

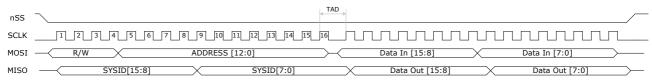

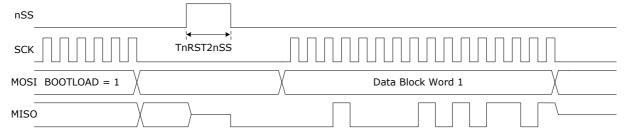

The beginning and end of an SPI transaction is illustrated in Figure 31.

All SPI transactions MUST be bounded by the Slave Select (nSS) line being driven low at their start and being driven high at their end. The SPI interface will not function if nSS is tied permanently low.

Figure 31 SPI data transfer

## 10.3 Register Access

The host operates the CAM204 CTU by writing to and reading from registers. There are a number of registers with different functions, as detailed in section 11. Each register is 16 bits wide, and has its own 12 bit address.

There are two modes of data transfer, *read* and *write read*. The host signals which transfer mode it wishes to use with the first 4 bits of an SPI transaction. A read starts with 0x0, and a write read with 0xF. The host then specifies the register address with the following 12 bits.

In a read operation, the next 16 bits clocked out of MISO are the data contained in the register at the specified address. The CAM204 ignores the state of MOSI during data transfer.

In a write read operation, the data to be written to the specified address is sent after the address, and the data previously at that address is clocked out of MISO at the same time.

This sequence, for a single register access, is illustrated in Figure 32.

A time TAD is required between the last address bit and first data bit clocked into the CAM204.

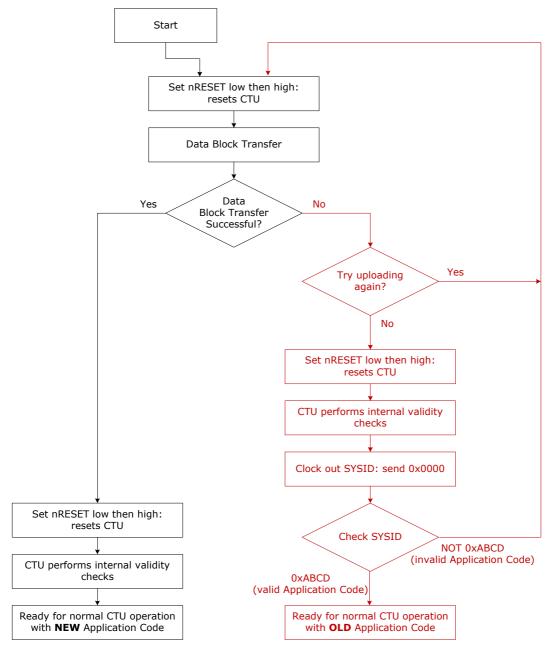

The CTU outputs the contents of its SYSID register (section 11.8) as the first word of each SPI transaction. This defaults to 0xABCD, and may be changed by the host. It is recommended that the host checks the value read back against the expected value as a test for SPI communication integrity.

Figure 32 single register access

Instead of accessing a single register, the host may access a set of consecutive registers by extending the SPI transaction as illustrated in Figure 33. Data is transferred one register at a time, starting at the first, specified address.

Registers are arranged in blocks dedicated to system functions, and to each sensor connected, see section 11. Multiple register access may not span across different blocks.

It is not essential to transfer complete 16 bit words into the CAM204. However it is recommended, since data from any incomplete word will be discarded. A delay TWW is required between the rising edge of SCK that clocks out the LSB of adjacent data words. These timings are illustrated in Figure 33 and specified in Table 22.

If the host attempts to access a reserved or unimplemented address, incoming data will be discarded and the state of MISO is undefined.

Figure 33 multiple register access

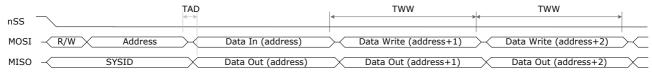

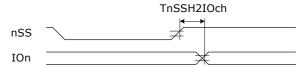

### 10.4 SPI Flag Clearing

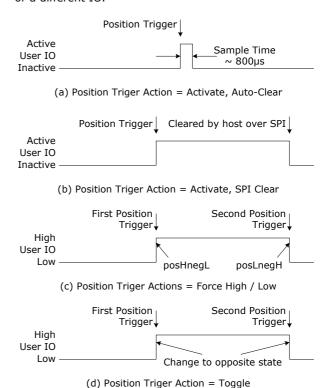

User configurable CTU output lines can be configured as sample indicators which indicate when the CTU has new (or new valid) position data available for a sensor. They may also be configured as position triggers.

There are different mechanisms to clear these signals. One is for the host to clear flags with an SPI transaction, illustrated in Figure 34. There is a delay between the end of the SPI transaction and the IO state change, TnSSH2IOch, specified in Table 22.

TnSSH2IOch takes different values depending on the registers written by the host. The CTU's response is

faster when the SIF or PTF bits are cleared (see sections 11.9 and 11.10). The response takes longer when IO functions are modified (e.g. changes to SIC, PTAH, PTC and PTP registers).

Figure 34 IO reset with SPI transaction

## 10.5 Interface Timing Specifications

Table 22 specifies the timing parameter values for SPI interface transactions. Parameters are defined in Figure 31, Figure 32, Figure 33 and Figure 34. TVALIDCHECK is defined in Figure 40.

Table 22 interface timing specifications

| Parameter   | Description                                                                                  | Min | Тур | Max | Units |

|-------------|----------------------------------------------------------------------------------------------|-----|-----|-----|-------|

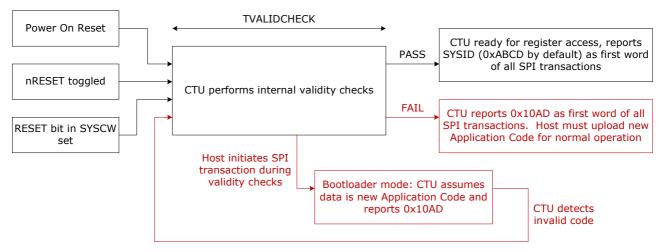

| TVALIDCHECK | Time for CTU internal validity checks following reset                                        | 12  | -   | 20  | ms    |

| TSCKL       | SCK Input Low Time                                                                           | 30  | -   | -   | ns    |

| TSCKH       | SCK Input High Time                                                                          | 30  | -   | -   | ns    |

| TSCK        | SCK clock period                                                                             | 100 | -   | -   | ns    |

| TSCKR       | SCK Input Rise Time                                                                          | _   | 10  | 25  | ns    |

| TSCKF       | SCK Input Fall Time                                                                          | -   | 10  | 25  | ns    |

| TMISOR      | MISO Rise Time (50pF load)                                                                   | -   | -   | 25  | ns    |

| TMISOF      | MISO Fall Time (50pF load)                                                                   | -   | -   | 25  | ns    |

| TMOSIV2SCKH | MOSI Setup Time                                                                              | 20  | -   | -   | ns    |

| TSCKH2MOSIX | MOSI Hold Time                                                                               | 20  | -   | -   | ns    |

| TSCKL2MISOV | MISO valid after SCK edge                                                                    | -   | -   | 30  | ns    |

| TnSSL2MISOV | MISO valid after nSS edge                                                                    | -   | -   | 5   | μs    |

| TnSSH2MISOZ | nSS high to MISO high Z                                                                      | -   | -   | 2   | μs    |

| TnSSL2SCKH  | nSS low to SCK edge                                                                          | 5   | -   | -   | μs    |

| TSCKL2nSSH  | Last SCK edge to nSS high                                                                    | 11  | -   | -   | μs    |

| TAD         | Idle time between address end and first data start                                           | 7   | -   | -   | μs    |

| TWW         | Data word to data word interval                                                              | 20  | -   | -   | μs    |

| TnSSH2nSSL  | nSS high time following read of register(s)                                                  | 6   | -   | -   | μs    |

|             | nSS high time following write to register(s) controlling IO, LED or DAC configuration        | 200 | -   | -   | μs    |

|             | nSS high time, any other SPI transaction                                                     | 40  | -   | -   | μs    |

| TnSSH2IOch  | Time to clear an IO by clearing SIF or PTF bits                                              | -   | -   | 40  | μs    |

|             | Time to change an IO following write to register(s) controlling IO, LED or DAC configuration | -   | -   | 200 | μs    |

## 10.6 Timing SPI Transactions and Position Measurements

An SPI transaction may occur while a position measurement is in progress. However, if it does, the position measurement may be abandoned and restarted. It is preferable to time SPI transactions and position measurements so that they do not coincide. This can be done by connecting using sample indicators, see section 12.7.

Alternatively, where maximum speed is not critical, SPI transactions may be separated by sufficient time for measurements to have finished. That is, at least the Sample Time (defined in section 12.8, sensor Type specific) plus adequate margin, per sensor.

# 11 Register Description

The host configures and controls the CAM204 CTU by writing to its internal registers. It determines status and measurement results by reading back from internal registers. This section describes the function of each of the CTU's registers.

Reading and writing to registers is done over the SPI interface, using the procedures described in section 10. Section 12 describes how to control the CTU to perform sensor position measurements, and how to configure the CTU's IO pins to implement position trigger signals.

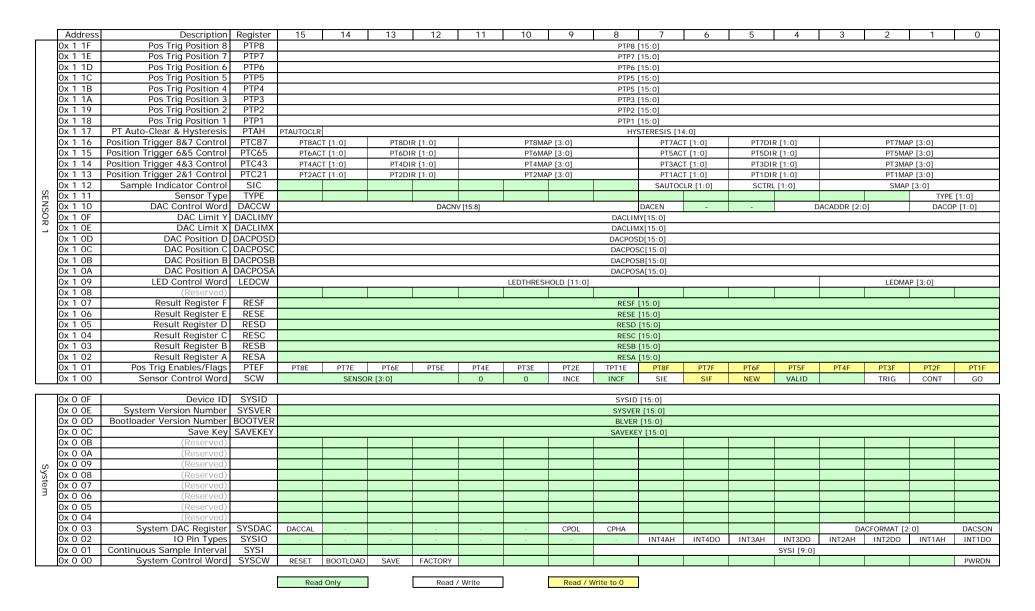

The CTU's register map is arranged in to distinct sections: a system control section and one section for each sensor. The arrangement for a 4 sensor system is illustrated in Figure 35 and Figure 36.

The map has been arranged to reduce SPI overheads once the whole system has been initialised (following a reset). Once initialised, the host system will normally only need to access a small contiguous block of registers to control each sensor, which can be performed within a single SPI transaction.

|          | Address | Register |

|----------|---------|----------|

|          | 0x 4 1F |          |

|          | 0x 4 1E | PTP7     |

|          | 0x 4 1D | PTP6     |

|          | 0x 4 1C | PTP5     |

|          | 0x 4 1B | PTP4     |

|          | 0x 4 1A | PTP3     |

|          | 0x 4 19 | PTP2     |

|          | 0x 4 18 | PTP1     |

|          | 0x 4 17 | PTAH     |

|          | 0x 4 16 |          |

|          | 0x 4 15 | PTC65    |

|          | 0x 4 14 | PTC43    |

|          | 0x 4 13 | PTC21    |

|          | 0x 4 12 | SIC      |

| SE       | 0x 4 11 | TYPE     |

| SN       | 0x 4 10 | DACCW    |

| Õ        |         | DACLIMY  |

| SENSOR 4 | 0x 4 0E | DACLIMX  |

|          |         | DACPOSD  |

|          | 0x 4 0C | DACPOSC  |

|          | 0x 4 0B | DACPOSB  |

|          | 0x 4 0A | DACPOSA  |

|          | 0x 4 09 | LEDCW    |

|          | 0x 4 08 |          |

|          | 0x 4 07 | RESF     |

|          | 0x 4 06 | RESE     |

|          | 0x 4 05 | RESD     |

|          | 0x 4 04 | RESC     |

|          | 0x 4 03 | RESB     |

|          | 0x 4 02 | RESA     |

|          | 0x 4 01 | PTEF     |

|          | 0x 4 00 | SCW      |

|          |                    | Register |

|----------|--------------------|----------|

|          | 0x 3 1F            | PTP8     |

|          | 0x 3 1E<br>0x 3 1D | PTP7     |

|          | 0x 3 1D            | PTP6     |

|          | 0x 3 1C            | PTP5     |

|          | 0x 3 1B            | PTP4     |

|          | 0x 3 1A            | PTP3     |

|          | 0x 3 19            | PTP2     |

|          | 0x 3 18            | PTP1     |

|          | 0x 3 17            | PTAH     |

|          | 0x 3 16            | PTC87    |

|          | 0x 3 15            | PTC65    |

|          | 0x 3 14            | PTC43    |

|          | 0x 3 13            | PTC21    |

|          | 0x 3 12            | SIC      |

| SENSOR 3 | 0x 3 11            | TYPE     |

| SN       | 0x 3 10            | DACCW    |

| Ö        | 0x 3 0F            | DACLIMY  |

| 3        | 0x 3 0E<br>0x 3 0D | DACLIMX  |

|          | 0x 3 0D            | DACPOSD  |

|          | 0x 3 0C            | DACPOSC  |

|          | 0x 3 0B            | DACPOSB  |

|          | 0x 3 0A            | DACPOSA  |

|          | 0x 3 09<br>0x 3 08 | LEDCW    |

|          | 0x 3 08            |          |

|          | 0x 3 07            | RESF     |

|          | 0x 3 06            | RESE     |

|          | 0x 3 05            | RESD     |

|          | 0x 3 04            | RESC     |

|          | 0x 3 03            | RESB     |

|          | 0x 3 02            | RESA     |

|          | 0x 3 01            | PTEF     |

|          | 0x 3 00            | SCW      |

|          |                    |          |

|          |                               | Register |

|----------|-------------------------------|----------|

|          | 0x 2 1F                       | PTP8     |

|          | 0x 2 1E                       | PTP7     |

|          | 0x 2 1D                       | PTP6     |

|          | 0x 2 1C                       | PTP5     |

|          | 0x 2 1B                       | PTP4     |

|          | 0x 2 1A<br>0x 2 19            | PTP3     |

|          | 0x 2 19                       | PTP2     |

|          | 0x 2 18                       | PTP1     |

|          | 0x 2 17                       | PTAH     |

|          | 0x 2 16                       | PTC87    |

|          | 0x 2 15                       | PTC65    |

|          | 0x 2 14                       | PTC43    |

|          | 0x 2 13                       | PTC21    |

|          | 0x 2 12                       | SIC      |

| SENSOR 2 | 0x 2 11<br>0x 2 10<br>0x 2 0F | TYPE     |

| S        | 0x 2 10                       | DACCW    |

| Ö        | 0x 2 0F                       | DACLIMY  |

| 70       | 0x 2 0E                       | DACLIMX  |

|          | 0x 2 0D                       | DACPOSD  |

|          | 0x 2 0C                       | DACPOSC  |

|          | 0x 2 0B                       | DACPOSB  |

|          | 0x 2 0A                       | DACPOSA  |

|          | 0x 2 09                       | LEDCW    |

|          | 0x 2 08                       |          |

|          | 0x 2 07                       | RESF     |

|          | 0x 2 06                       | RESE     |

|          | 0x 2 05                       | RESD     |

|          | 0x 2 04                       | RESC     |

|          | 0x 2 03                       | RESB     |

|          | 0x 2 02                       | RESA     |

|          | 0x 2 01                       | PTEF     |

|          | 0x 2 00                       | SCW      |

|              |         | Б        | 6                            |  |  |  |  |  |  |  |  |

|--------------|---------|----------|------------------------------|--|--|--|--|--|--|--|--|

|              |         | Register | Description                  |  |  |  |  |  |  |  |  |

|              | 0x 1 1F | PTP8     | Pos Trig Position 8          |  |  |  |  |  |  |  |  |

|              | 0x 1 1E | PTP7     | Pos Trig Position 7          |  |  |  |  |  |  |  |  |

|              |         | PTP6     | Pos Trig Position 6          |  |  |  |  |  |  |  |  |

|              | 0x 1 1C | PTP5     | Pos Trig Position 5          |  |  |  |  |  |  |  |  |

|              | 0x 1 1B | PTP4     | Pos Trig Position 4          |  |  |  |  |  |  |  |  |

|              | 0x 1 1A | PTP3     | Pos Trig Position 3          |  |  |  |  |  |  |  |  |

|              |         | PTP2     | Pos Trig Position 2          |  |  |  |  |  |  |  |  |

|              |         | PTP1     | Pos Trig Position 1          |  |  |  |  |  |  |  |  |

|              |         | PTAH     | PT Auto-Clear & Hysteresis   |  |  |  |  |  |  |  |  |

|              | 0x 1 16 | PTC87    | Position Trigger 8&7 Control |  |  |  |  |  |  |  |  |

|              | 0x 1 15 | PTC65    | Position Trigger 6&5 Control |  |  |  |  |  |  |  |  |

|              | 0x 1 14 | PTC43    | Position Trigger 4&3 Control |  |  |  |  |  |  |  |  |

|              | 0x 1 13 | PTC21    | Position Trigger 2&1 Control |  |  |  |  |  |  |  |  |

|              | 0x 1 12 | SIC      | Sample Indicator Control     |  |  |  |  |  |  |  |  |

| SENSOR       | 0x 1 11 | TYPE     | Sensor Type                  |  |  |  |  |  |  |  |  |

| SS           | 0x 1 10 | DACCW    | DAC Control Word             |  |  |  |  |  |  |  |  |

| Š            | 0x 1 0F | DACLIMY  | DAC Limit Y                  |  |  |  |  |  |  |  |  |

| <del>2</del> | 0x 1 0E | DACLIMX  | DAC Limit X                  |  |  |  |  |  |  |  |  |

|              | 0x 1 0D | DACPOSD  | DAC Position D               |  |  |  |  |  |  |  |  |

|              | 0x 1 0C | DACPOSC  | DAC Position C               |  |  |  |  |  |  |  |  |

|              | 0x 1 0B | DACPOSB  | DAC Position B               |  |  |  |  |  |  |  |  |

|              | 0x 1 0A | DACPOSA  | DAC Position A               |  |  |  |  |  |  |  |  |

|              | 0x 1 09 | LEDCW    | LED Control Word             |  |  |  |  |  |  |  |  |

|              | 0x 1 08 |          | (Reserved)                   |  |  |  |  |  |  |  |  |

|              | 0x 1 07 | RESF     | Result Register F            |  |  |  |  |  |  |  |  |

|              | 0x 1 06 | RESE     | Result Register E            |  |  |  |  |  |  |  |  |

|              | 0x 1 05 | RESD     | Result Register D            |  |  |  |  |  |  |  |  |

|              | 0x 1 04 | RESC     | Result Register C            |  |  |  |  |  |  |  |  |

|              | 0x 1 03 | RESB     | Result Register B            |  |  |  |  |  |  |  |  |

|              | 0x 1 02 | RESA     | Result Register A            |  |  |  |  |  |  |  |  |

|              | 0x 1 01 | PTEF     | Pos Trig Enables/Flags       |  |  |  |  |  |  |  |  |

|              | 0x 1 00 | SCW      | Sensor Control Word          |  |  |  |  |  |  |  |  |

|              |         |          |                              |  |  |  |  |  |  |  |  |

|        | 1       |         |                            |

|--------|---------|---------|----------------------------|

|        | 0x 0 0F | SYSID   | Device ID                  |

|        | 0x 0 0E | SYSVER  | System Version Number      |

|        | 0x 0 0D | BOOTVER | Bootloader Version Number  |

|        | 0x 0 0C | SAVEKEY | Save Key                   |

|        | 0x 0 0B |         | (Reserved)                 |

|        | 0x 0 0A |         | (Reserved)                 |

| S      | 0x 0 09 |         | (Reserved)                 |

| ys     | 0x 0 08 |         | (Reserved)                 |

| System | 0x 0 07 |         | (Reserved)                 |

| ゴ      | 0x 0 06 |         | (Reserved)                 |

|        | 0x 0 05 |         | (Reserved)                 |

|        | 0x 0 04 |         | (Reserved)                 |

|        | 0x 0 03 | SYSDAC  | System DAC Register        |

|        | 0x 0 02 | SYSIO   | IO Pin Types               |

|        | 0x 0 01 | SYSI    | Continuous Sample Interval |

|        | 0x 0 00 | SYSCW   | System Control Word        |

Figure 35 Register map overview

Figure 36 Register map detail

# 11.1 SYSCW: System Control Word

| SYSCW  | 15    | 14       | 13   | 12      | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|----------|------|---------|----|----|---|---|---|---|---|---|---|---|---|-------|

| 0x000  | RESET | BOOTLOAD | SAVE | FACTORY | -  | -  | 1 | - | 1 | 1 |   | 1 | 1 | ı | 1 | PWRDN |

| Access | R/W   | R/W      | R    | R       | R  | R  | R | R | R | R | R | R | R | R | R | R/W   |

Factory default value = 0x0000

Writing a 1 to the RESET bit will result in a device reset at the end of the SPI transaction. Registers will return to their default values and measurements will be aborted. SPI transactions will be ignored until the device comes out of reset.

Writing a 1 to the PWRDN bit pauses measurements in progress and puts the CTU into a low power state. To take the CTU out of this state and resume any measurements in progress, toggle nSS low. This operation may take the form of a dummy SPI read, whose results should be discarded.

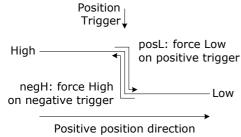

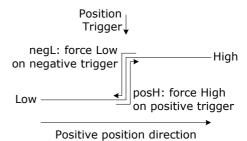

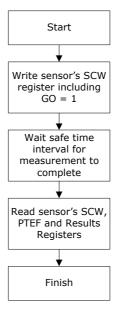

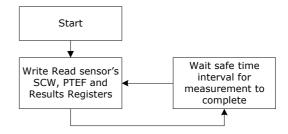

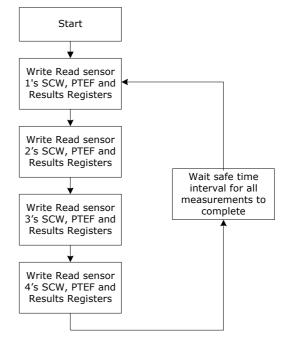

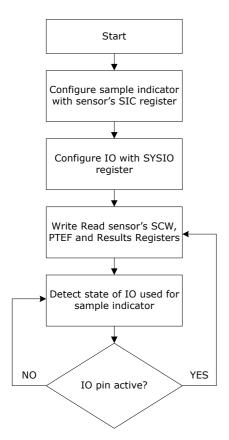

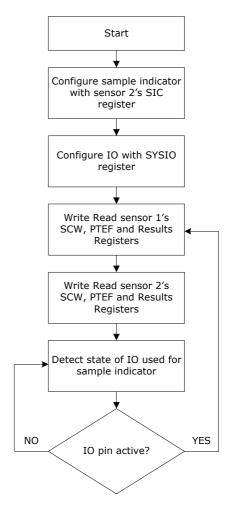

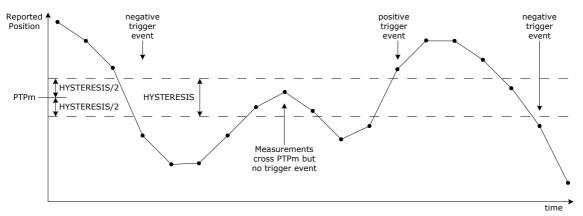

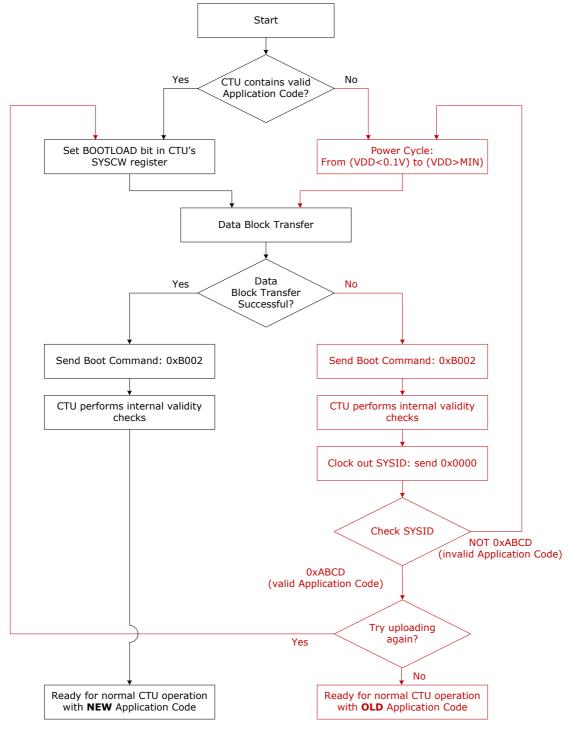

Writing a 1 to the BOOTLOAD bit resets the CTU at the end of the SPI transaction. When the CTU comes out of reset, it will remain in Bootloader Mode (section 14.6) until the next reset.